La porte logique OU

Cette fiche vous propose de modéliser en utilisant sur la solution LTspice une porte logique OU à l'aide de deux diodes à commutation et de la simuler pour déterminer son mode de fonctionnement ainsi que sa table de vérité.

Modélisation d'une porte logique avec deux diodes à commutation 1N4148

A l'aide de la solution LTSpice, modélisez le schéma électrique proposé ci-dessous :

Configurez maintenant la valeur de la résistance, notre dipôle récepteur, sous LTSpice telle que R soit égale à 1KΩ.

Configurez maintenant la valeur de la résistance, notre dipôle récepteur, sous LTSpice telle que R soit égale à 1KΩ.

Sélectionnez ensuite la référence 1N4148 pour les deux diodes D1 et D2 comme vous l'explique l'image ci-dessous:

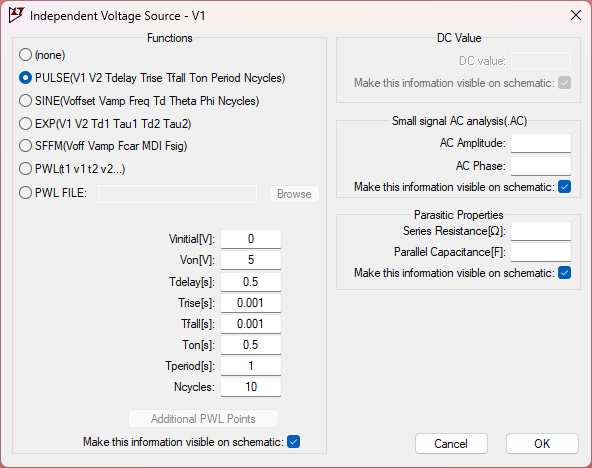

Enfin, pour modéliser les deux interrupteurs A et B, nous allons utiliser sous LTspice deux sources de tension dont la forme est un signal carré d'amplitude 5V, de même fréquence mais décalées dans le temps à 0.5 seconde. Pour cela, nous allons configurer deux sources de tension V1 et V2 autant que deux générateurs de tension décalé à à une 1/2 période de temps de la fréquence prévue. Soit pour chaque seconde, nous obtiendrons deux états logiques tels que:

- une demi-période d'une durée 0.5s pour l'état "0"

- et une demi-période d'une duére de 0.5s pour l'état "1".

Pour réaliser les différentes combinaisons possible entre les deux interrupteurs A et B, nous allons différer un signal électrique V2 par rapport à V1 en le décalant de 0.25 seconde.

Pour cela, la source de notre générateur V1 sera configurée comme le démontre la capture ci-dessous:

et pour le second générateur V2 comme suit:

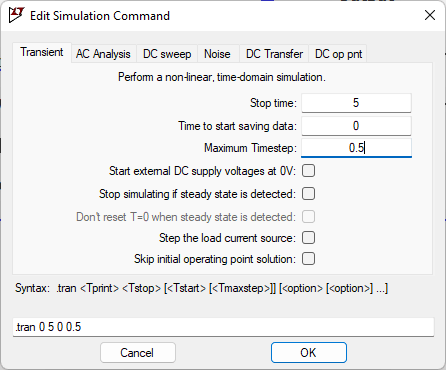

Ainsi, nous pouvons lancer la simulation sous LTSpice tout en mode Transient :

Et pour visualisez le résultat attendu, ajoutez dans le même graphe les deux traces V1 et V2 et la sortie VR. A l'aide du taleau ci-dessous, récupérez les différentes valeurs de VR en fonction des différents états de A et de B:

| A | B | S = A OU B (VR) |

| 0 | 0 | |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 |

Que remarquez-vous ?

Réalisation et analyse

En partant du circuit électrique proposé dans l'énoncé de cette fiche ci-dessus, et comme expliqué auparavant pour la modélisation des deux interrupteurs A et B par deux sources de tension de type PULSE sous LTspice, notre schéma modélisé dans l'application de simulation sera comme suit :

Configurons maintenant les différentes composants avec les valeurs indiquées dans la description de cette fiche telles que:

- R1 = 1KΩ.

- V1 et V2 ave la configuration proposées pour obtenir les deux signaux électriques différés à 0.25s.

- les deux diodes D1 et D2 à la référence 1N4148.

Une fois que notre projet est prêt, nous pouvons lancer la simulation sous LTspice dans le mode de simulation décrit :

Une fois que la simulation est prête, autrement dit que notre simulateur a terminé ses calculs, nous pouvons ajouter manuellement les trois variables de notre circuit V1, V2 et V_out dans trois traces différentes comme le démontre la capture ci-dessous :

Analysons maintenant ces 3 coubres, nous pouvons constater :

- Si V(n001) = 0 ⇒ A = 0 et si V(n001) = 5V ⇒ A = 1

- Si V(n003) = 0V ⇒ B = 0 et si V(n003) = 5V ⇒ B = 1

- Si V_out (représenté par V(n002)) = 0V ⇒ S = 0 et si V_out ≅ 5V ⇒ S = 1 (la valeur V_out en volt dépend principalement des caractéristiques de la diode à comutation choisie pour la réalisation de cette porte logique OU).

L'image ci-dessous vous explique cela :

Récupérons maintenant les différentes valeurs de VR en fonction des différents états possible des deux interrupteurs A et de B :

| A | B | S = A OU B (VR) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Ainsi, nous retrouvons la porte logique OU, appelée également OR en anglais. Cette porte logique qui a toujours une sortie S vrai si l'une des de ces entrées est égale à 1.