La porte logique NON

Une porte logique, appelée aussi porte logique électronique, est un composant électrique en électronique numérique élémentaire qui nous permet d'effectuer une opération logique élémentaire ou complexe sur un ou plusieurs digits (appelé aussi bit).

Dans cette fiche, nous allons découvrir ensemble la porte logique NON à l'aide de la modélisation de cette fonction en utilisant un transistor NPN 2N3904 et deux résistances sous la solution de simulation LTSpice. Nous analysons ensemble les différents modes de fonctionnement ainsi que le comportement de cette porte logique en fonction de la valeur du signal électrique à l'entrée de ce composant.

Modélisation d'une porte logique avec un transistor NPN

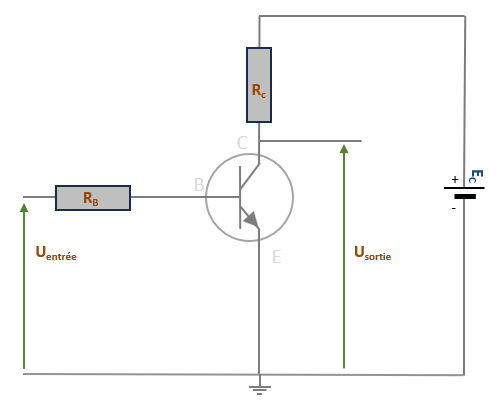

A l'aide de la solution LTSpice XIII, modélisez le schéma électrique ci-dessous :

Configurez ensuite les différents élements de ce circuit sous LTSpice pour les valeurs suivantes :

- Uentrée = Ec = 5V

- RB = 1KΩ.

- RC = 10KΩ.

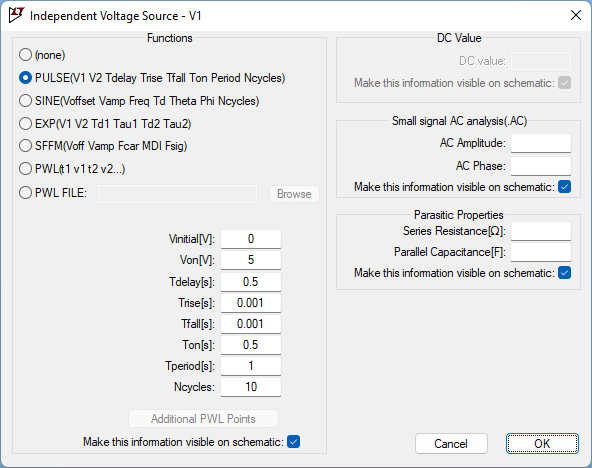

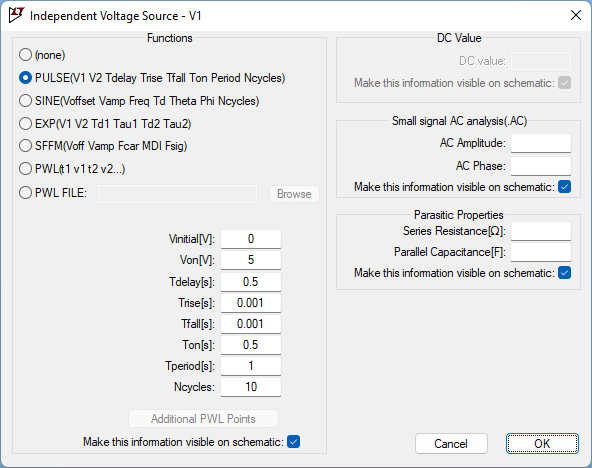

Comme nous sommes entrain de modéliser une porte logique, nous allons configurer la tension Uentrée à un signal carré d'amplitude 5V et d'une fréquence de valeur 1 Hertz (Hz) telle que la période de chaque états "0" ou "1" soit égale à la valeur de 0.5s. Pour cela, la source de notre générateur doit être configurée comme suit:

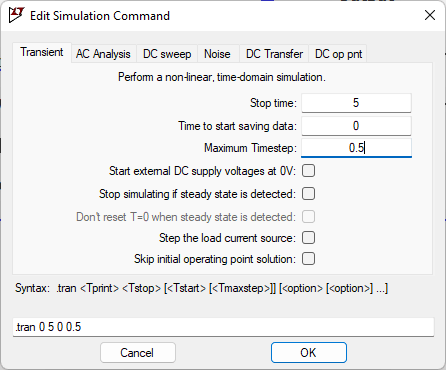

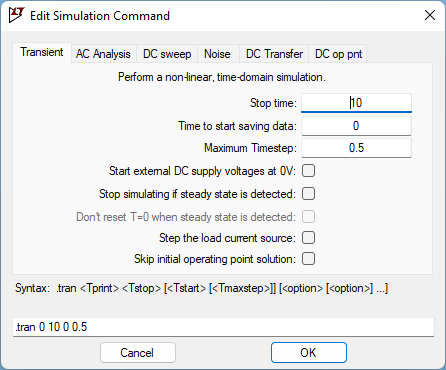

Vous pouvez maintenant lancer la simulation sous LTSpice tout en choisisant la commande DC op pnt telle que :

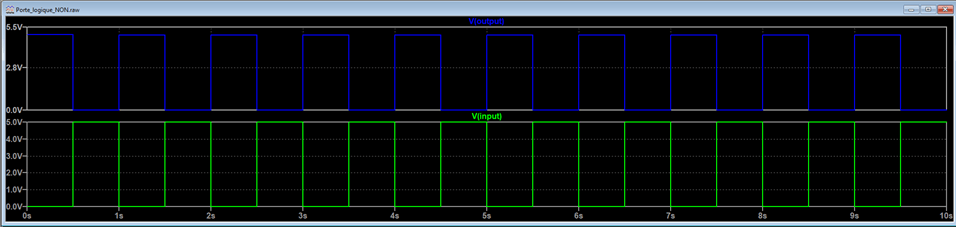

Une fois que la simulation est terminée, ajoutez dans le même graphe, les deux traces Uentrée et Usortie mais dans deux traces différentes pour pouvoir analyser la fonction globale de cette porte logique.

Que constatez-vous ? Que pouvons-nous conclure ?

Réalisation et méthodologie

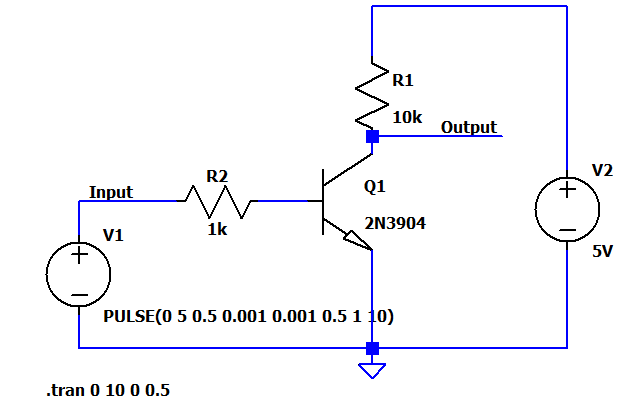

En suivant le schéma électrique proposé par ce TD, nous pouvons modéliser notre schéma sous LTSpice comme suit :

Modélisez la source de votre signal d'entrée comme indiqué dans l'énoncé comme suit :

Vous pouvez maintenant lancer la simulation sous LTspice avec la configuration suivant pour notre simulateur:

Une fois le calcul de notre simulateur est terminé, ajoutez les deux points déjà modélisés dans notre circuit Vinput et Voutput dans deux traces différentes comme suit :

Si nous considérons l'hypothèse suivante, que si :

- Vinput = 0V (soit Uentrée dans l'énoncé de ce TD) représente la valeur binaire "0" et,

- Voutput ≅ 5V (soit Usortie dans l'énoncé de ce TD) représente la valeur binaire "1",

nous pouvons en déduisons, à partir de ces deux courbes Vinput et Voutput, que l'information à la sortie est toujours l'inverse de l'information à l'entrée de notre module.

Ainsi, ce schéma électrique simple constitué à partir d'un transistor NPN 2N3904 et de deux résistances représente bien la porte logique NON