La porte logique ET

Cette fiche vous permet de modéliser, sous la solution de simulation de schéma électronique LTspice, à l'aide de deux diodes à jonction une porte logique ET, puis de l'analyser et de comprendre son fonctionnement.

Modélisation d'une porte logique avec deux diodes à jonction 1N4007

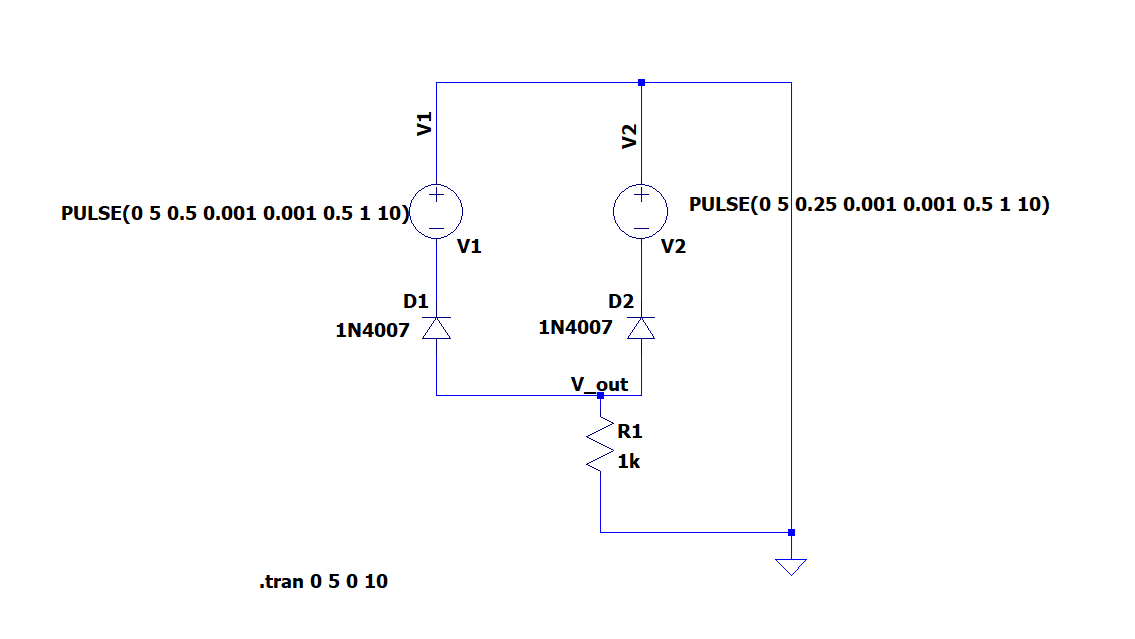

A l'aide de la solution LTSpice, réalisez le schéma électrique ci-dessous :

Configurez maintenant le seul élement de notre circuit sous LTSpice telle que la résistance soit égale à R = 1KΩ.

Configurez maintenant le seul élement de notre circuit sous LTSpice telle que la résistance soit égale à R = 1KΩ.

Sélectionnez, ensuite, la référence 1N4007 pour les deux diodes D1 et D2 comme vous le démontre la fenêtre "Select Diode" ci-dessous:

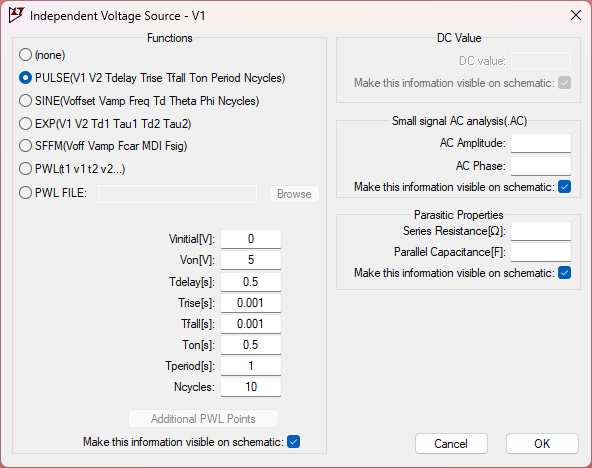

Et enfin, pour modéliser les deux interrupteurs A et B sous LTspice, nous allons les remplacer par deux sources de signal carrée d'amplitude 5V, de même fréquence mais décalées dans le temps. Pour cela, nous allons modéliser deux sources de tensions V1 et V2 comme deux générateurs de tension à un signal carré d'amplitude 5V et de fréquence 1 Hertz. Soit chaque seconde, nous obtiendrons deux états logiques tels que:

- une demi-période d'une durée 0.5s pour l'état "0"

- et une demi-période d'une duére de 0.5s pour l'état "1".

Pour obtenir les différentes combinaisons entre A et B, nous allons différer V2 par rapport à V1 en le décalant de 0.25s.

Pour cela, la source de notre générateur doit être configurée comme suit pour V1

et pour V2 comme suit:

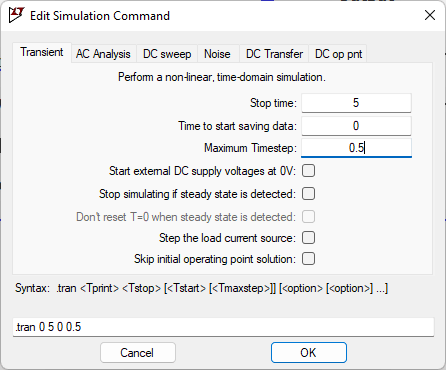

Ainsi, vous pouvez lancer la simulation sous LTSpice tout en choisisant la commande Transient telle que :

Ajoutez dans le même graphe, les deux traces V1 et V2 et le signal à la sortie VR. A l'aide du tableau ci-dessous, récupérez les différentes valeurs de VR en fonction des différents états de A et de B:

| A | B | S = A ET B (VR) |

| 0 | 0 | |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 |

Que remarquez-vous ?

Réalisation et méthodologie

En se reférent au circuit électrique proposé ci-dessus, et en remplaçant les deux interrupteurs A et B par deux sources de tension de type PULSE sous LTspice, nous pouvons modéliser notre schéma électrique comme suit :

Configurons maintenant les différentes composants avec les valeurs demandées telles que:

- R = 1KΩ.

- V1 et V2 ave les valeurs fournies pour obtenir les deux signaux carrés différés.

- les deux diodes D1 et D2 à la référence 1N4007.

Nous pouvons maintenant lancer la simulation sous LTspice avec la configuration suivant pour notre simulateur:

Dès que notre simulateur a terminé de calculer, nous pouvons ajouter les trois variables modélisées dans notre circuit V1, V2 et V_out dans trois traces différentes comme suit :

Remplissons maintenant le tableau demandé comme suit:

- Si V1 (représentée par V(n001)) = -5V ⇒ A = 0 et si V1 = 0V ⇒ A = 1

- Si V2 (représentée par V(n002)) = -5V ⇒ B = 0 et si V2 = 0V ⇒ B = 1

- Si V_out = ≅ -5V ⇒ S = 0 et si V_out = 0V ⇒ S = 1 (la valeur V_out dépend essentiellement des caractéristiques de la diode à jonction utilisée pour concevoir la porte logique).

L'image ci-dessous vous explique cela :

récupérez les différentes valeurs de VR en fonction des différents états de A et de B :

| A | B | S = A ET B (VR) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Ainsi, nous retrouvons la porte logique ET, ou l'opérateur AND en anglais. Cette porte logique qui ne valide la sortie S que si seulement toutes ces entrées sont égales à 1.